←シラバスページへ

《第10回の講義の内容・感想》

今回の講義はかなり充実していた。曽我氏のトーク&レジメ&PowerPoint(?)からいろいろな事を学んだ。しかしそれは同時に 「内容をWeb化するのには多大な時間と労苦を要する」という事を意味する。制作者にとっては実にショッキングな事だ。(-_-; 「レジメを丸ごとスキャナにかけてそのまま掲載したい」という欲望を抑えつつ私は必死にキーを叩くのであった・・・。 ところで第10回講義は前回の講義の続き的な内容から半導体メモリーへと発展している。 初めてだからということもあるが,やはり半導体メモリーの内容は若干難しく感じられる。曽我氏もこの項目については特に しっかり学習して欲しいらしく,カラーの資料を用意するほどの熱の入れようだ。

《分かったこと》

クロック

クロック(正確にはクロックパルス)とは簡単に言うと半導体の動作をコントロールする信号のことだ。水晶発振器から正確な周期で取り出され,フリップフロップ(以下FF)はクロックに歩調を合わせて動作する。前回説明したSRFFにはまだクロックが導入されていない。そのためFFを相互接続する回路では信号がダラダラとケジメのない伝播をするだけである。FFが真に実用になるのはクロックを導入 してからである。クロックを導入するとFFはそれに合わせてキチッキチッと動作する。

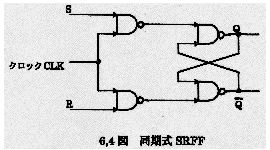

同期式SRFF

下図にクロックを導入した同期式SRFFを示す。クロックを導入したことによって動作は以下のようになる。

- FFへの入力信号S,Rが効力を持つのはクロック="1"(=5V)の時だけ

- S,R信号の到着時刻にばらつきがあってもクロック信号がないとFFは動作しない

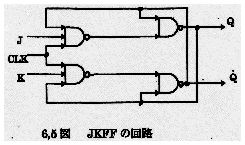

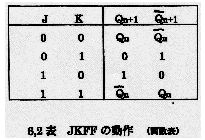

JKFF

SRFFはS,Rに"1"を与える事が禁止されているという制約がある。このため,回路の一部を変更してこの制約を取り除いたのが JKFFである。下にはJKFFの回路図及び動作表を示す。

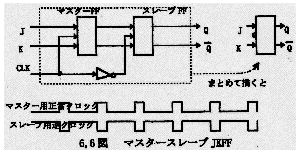

マスタースレーブJKFF(真の実用的FF)

このJKFFは1つをマスター,もう1つをスレーブとして2個のJKFFを一体化し,見かけ上1個のJKFFとして使用し,信号伝播の安定化 を図ったものである(下図を参照)。この時マスターには普通のクロックパルスを,スレーブには反転したクロックパルスを与えるのがミソである。このようにすると,クロックの途中で出力が出現してしまうという不具合を解消することができる。

半導体メモリー

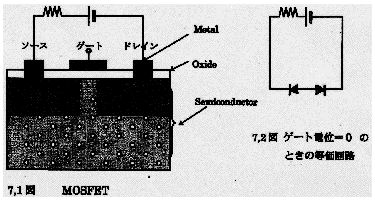

コンピューターの主記憶装置のメモリー素子としては,最初の20年間は磁気コア素子が使われたが,今では半導体メモリーが圧倒的 多数で使われている。半導体メモリーで用いられるトランジスタはMOS-FET(Metal Oxide Semiconductor - Field Effect Transistor) である。これは以前説明した接合型トランジスタとは動作の仕方が違う。

MOSトランジスタ

"MOS"とは構造上の名前であり,"FET"は動作原理上の名前である。下にMOSトランジスタの図を示す。図を見てみると表面から 名前の通りにMetal(金属),Oxide(酸化膜),Semiconductor(半導体)と重なっていることが分かる。ソース端子とドレイン端子の 間にスイッチがあると想定し,それをゲート端子に加える電圧によってON/OFFする。さらにその隣にはMOSトランジスタの回路図を 示す。

DRAM

DRAMは先程説明したMOS-FETにコンデンサを取り付けたものをマトリックス状に展開したものだ。(下図参照)動作等の詳しい事は次回のページで説明することにして,ここでサラッと言うとコンデンサに電荷が溜まっている場合に素子は"1"を記憶する。溜まっていない場合は逆に "0"を記憶している。

←授業選択画面に戻る

←鈴木研究室ホームへ