←シラバスページへ

《第8回の講義の内容・感想》

今回の講義は内容的に第7回の続きである。前回話した様々な論理回路の改良版が登場するといった感じだ。それにしても進度が気に なる。もう本来の予定とは遠くかけ離れているような気が・・・。最後の30分は演習が行われた。

《分かったこと》

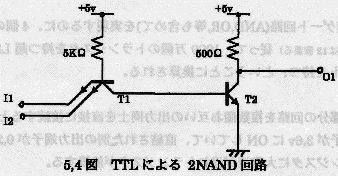

「TTLによる2入力NAND回路」

前回の最後に話したDTL(Diode Transistor Logic)回路を改良したものが下に示すTTL(Transistor Transistor Logic) による2入力NAND回路である。DTLでは独立したダイオードを複数設けていたが,半導体プロセスとしてはTTLのようにエミッタが2つある1つの トランジスタを制作した方がより簡単である。

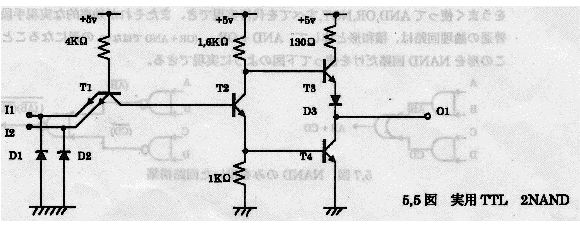

ところがこのTTL回路にもまだまだ改良すべき点が1つある。実はT2がOFFで出力に+5Vがながれる場合に不具合が起こってしまう。 現実的に考えて実際には出力端子にさらに他の回路が接続されているのだが,その場合に"0"か"1"をうまく判別することができない 状況に陥ってしまうのだ。この欠点を直したものが下図の回路だ。「実用的TTL」とでも呼ぶことにしようか。

「TTL NANDゲートの使い方」

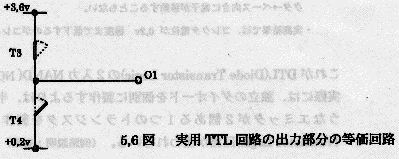

さらにTTL NAND回路の出力部分は下図のように等価な回路に置き換えて考えた方が分かりやすい。 このTTL回路の出力に他回路の入力を複数つなげると,一定の電流を維持できなくなる。10個の入力を つなぐのが正常限界とのことだ。 曽我氏はきっと「ちなみに」的な意味を込めてレジメに書いたのだろうが,このTTL回路の出力同士を 接続すると大電流によって壊れてしまうらしい。(ホントにおまけ的な話しだな,こりゃ。出力同士を 本気で接続してしまうお馬鹿さんなんているわけないよ・・・)

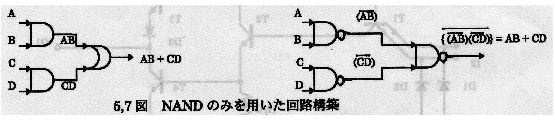

「3NAND 4NAND回路」

これまで2つの入力を持つNAND回路を説明してきたが,入力部分のトランジスタをマルチ化することで3つや4つといった たくさんの入力端子を持つNAND回路を作成することができる。下図がそれだ。実はこれ,回路を少し変形させるだけで AND,ORやNOTも演算できてしまうのだ。実に効率のイイ話じゃないか!!!

《まとめ》

- DTL NAND回路よりもTTL NAND回路の方が実用的である

- TTL NAND回路の出力端子には接続数に限界がある

《関連サイト-さらに詳しく調べたい方は下記のサイトヘどうぞ》

よさそうなサイトが見つからないんだよなぁ・・・。

←授業選択画面に戻る

←鈴木研究室ホームへ